AlphaAtlas

[H]ard|Gawd

- Joined

- Mar 3, 2018

- Messages

- 1,713

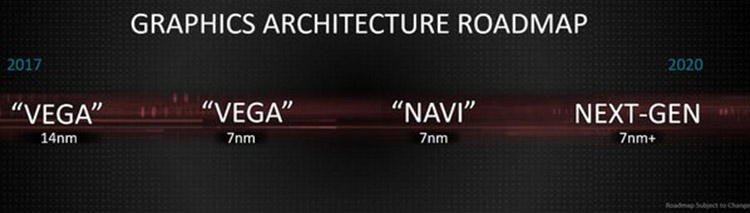

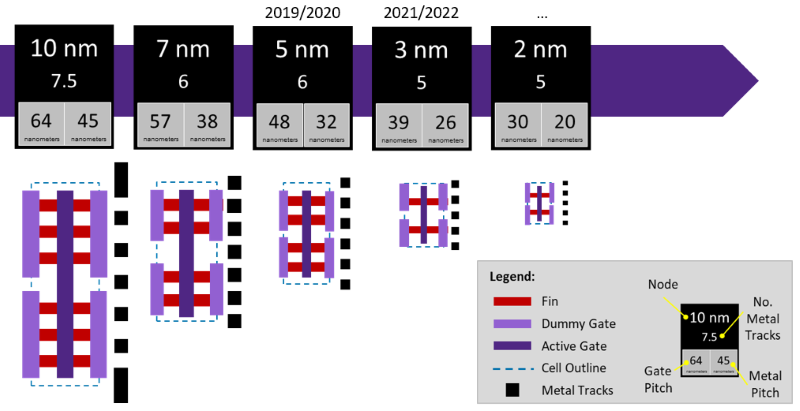

Last year, Taiwan Semiconductor, who is responsible for manufacturing all of AMD's recently announced 7nm products and will presumably make Nvidia's 7nm GPUs, said that they'll start 5nm production with full EUV in April 2019 last year. But making chips at bleeding edge nodes is a hard business, to say the least. Delays tend to arise when production problems rear their ugly heads, and bad economics can make transitions to a new node cost prohibitive. But fortunately, at their conference call this year, TSMC said that that their 5nm process is still on track for 1H 2019, and that they're already engaging with HPC and smartphone customers. With the recent decline in smartphone sales, and ever-changing trade tensions with China, TSMC stock has fallen significantly these past few months, and naturally, investors asked a lot of pointed questions. But TSMC seems confident that companies will aggressively adopt their 5nm and 7nm process anyway due to the significant performance advantages they will offer over older nodes. Mark Liu also mention that "almost all" of TSMC's customers want to adopt their relatively new advanced packaging services, meaning that multi-chip products like HBM GPUs or CPUs with an I/O die might be a more common sight on the 5nm node. He also mentioned that cryptocurrency mining had a significant impact on their business, one they didn't see coming last year. Thanks to Digitimes for spotting the conference call, even though they didn't link it.

Even with a slow year like 2019, we firmly believe AI and 5G are the megatrends that will drive the future semiconductor growth. And were affirm our long-term growth projection of 5% to 10% CAGR. Now I will talk about our 5-nanometer status. Our N5 technology development is well on track, with customer tapeout schedule for first half 2019 and volume production ramp in first half 2020. We are already in preparation for N5's ramp. All applications that are using7-nanometer today will adopt 5-nanometer. In addition, we are expecting the customer product portfolio at N5 and see expanding addressable market opportunities. We expect more applications in HPC to adopt N5. Thus we are confident that N5 will also be a large and long-lasting node for TSMC... 5-nanometer are ramping in 2020. I would expect that product portfolio is expanding more as compared with the 7-nanometer in 2018.

Even with a slow year like 2019, we firmly believe AI and 5G are the megatrends that will drive the future semiconductor growth. And were affirm our long-term growth projection of 5% to 10% CAGR. Now I will talk about our 5-nanometer status. Our N5 technology development is well on track, with customer tapeout schedule for first half 2019 and volume production ramp in first half 2020. We are already in preparation for N5's ramp. All applications that are using7-nanometer today will adopt 5-nanometer. In addition, we are expecting the customer product portfolio at N5 and see expanding addressable market opportunities. We expect more applications in HPC to adopt N5. Thus we are confident that N5 will also be a large and long-lasting node for TSMC... 5-nanometer are ramping in 2020. I would expect that product portfolio is expanding more as compared with the 7-nanometer in 2018.

![[H]ard|Forum](/styles/hardforum/xenforo/logo_dark.png)